Institut für Technik der Informationsverarbeitung **∏**√

#### Dr.-Ing. Jens Becker (jens.becker@kit.edu) Dipl.-Inform. Tanja Harbaum (harbaum@kit.edu)

Institut für Technik der Informationsverarbeitung (ITIV)

KIT – Universität des Landes Baden-Württemberg und nationales Forschungszentrum in der Helmholtz-Gemeinschaft

www.itiv.kit.edu

#### **Schedule CSP**

Monday: 09:45 – 11:15 (MTI)

- 24.04.2017 Lecture 1

- 01.05.2017 May Day

- 08.05.2017 Lecture 3

- 15.05.2017 Exercise 2

- 22.05.2017 Lecture 5

- 29.05.2017 Lecture 6

- 05.06.2017 Pentecost week

- 12.06.2017 Exercise 3

- 19.06.2017 Lecture 8

- 26.06.2017 Lecture 9

- 03.07.2017 Lecture 10

- 10.07.2017 Lecture 11

17.07.2017 - Lecture 12

24.07.2017 - Exercise 7

Thursday: 09:45 – 11:15 (EAS)

- 27.04.2017 Lecture 2

- 04.05.2017 Exercise 1

- 11.05.2017 Lecture 4

- 25.05.2017 Ascension Day

- 01.06.2017 No Lecture

- 08.06.2017 Pentecost week

- **15.06.2017 Corpus Christi**

- 22.06.2017 Exercise 4

#### 06.07.2017 – Exercise 5 13.07.2017 – Exercise 6

- 20.07.2017 Lecture 7

- 27.07.2017 Question time

#### Monday, 31.07.2017: CSP - EXAMINATION

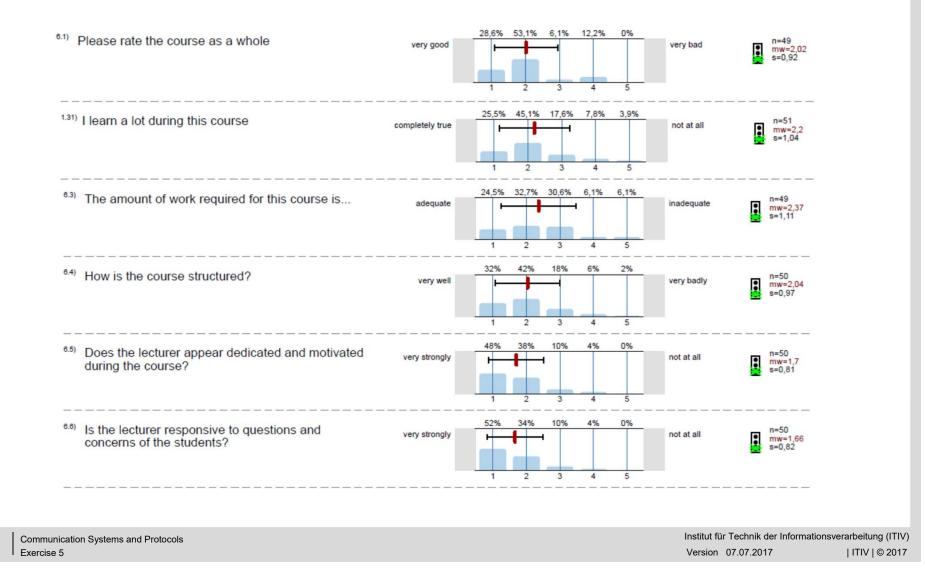

#### **Evaluation Results**

LQI: 100

3

#### **Evaluation Comments**

Many different topics, but non of them is realy discussed in detail

Lecture "only" gives an overview

- Tasks in problem sheet are formulated unclear!

- Unclear formulation tasks/statements

I'm sorry. We do our best!

As a computer scientist the hardware realisations are very hard to understand

We try to give you a brief introduction

### I<sup>2</sup>C-Bus (Inter-Integrated-Circuit-Bus)

- Serial Bus System

- Multi Master / Multi Slave

- CSMA/CA Arbitration Scheme

- Low Cost Bus System

. . .

5

### I<sup>2</sup>C-Bus

- Developed by Philips for interconnecting ICs on printed circuit boards

- Only two wires for data transmission

- Clock line SCL (serial clock)

- Data line SDA (serial data)

- Lower cost and error-prone because of low pin-count

- Multi-Master, Multi-Slave

- Data transmission in packets of 8bit

- 7bit for addresses  $\rightarrow$  128 addresses

- 1bit for toggling between reading/writing

- Transfer rate:

- 100kbit/s in standard mode

- 400kbit/s in fast mode

- 3.4Mbit/s in high-speed mode

Source of I<sup>2</sup>C images and diagrams: *NXP: UM10204, I2C-bus specification and user manual, Rev. 4 — 13 February 2012*

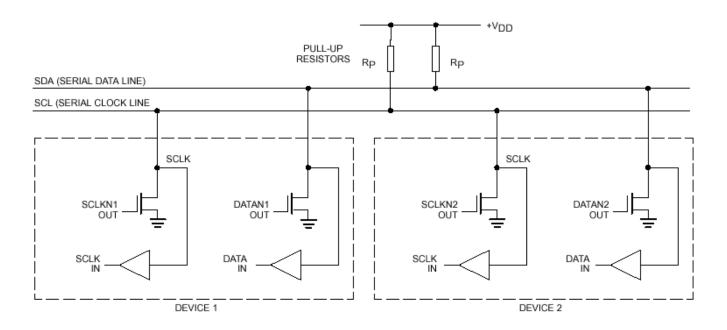

#### **I<sup>2</sup>C Bus Connection**

- Open-Collector outputs for every bus subscriber

- Wired-AND with dominant ,0' on the bus

- Pull-Up resistors externally connected

- In idle mode, both SCL and SDA are HIGH

- Concurrent monitoring of the bus at every subscriber

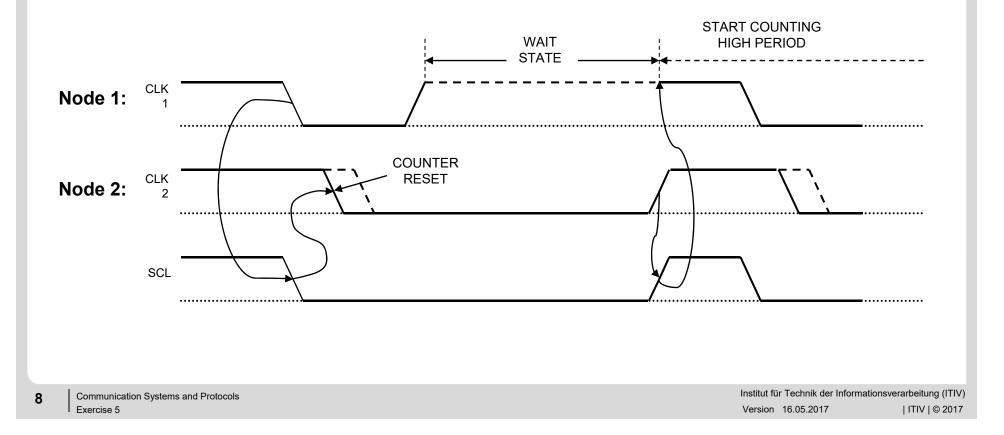

#### **Clock Synchronization**

- Clock signal is the sum generated by all nodes

- A slower node can pull down the bus to ,LOW' in order to insert wait states

- The next cycle is not started before SCL is back to ,HIGH'

# Task 1: I<sup>2</sup>C Synchronization

Communication Systems and Protocols Exercise 5

9

Institut für Technik der Informationsverarbeitung (ITIV) Version 07.07.2017 | ITIV | © 2017

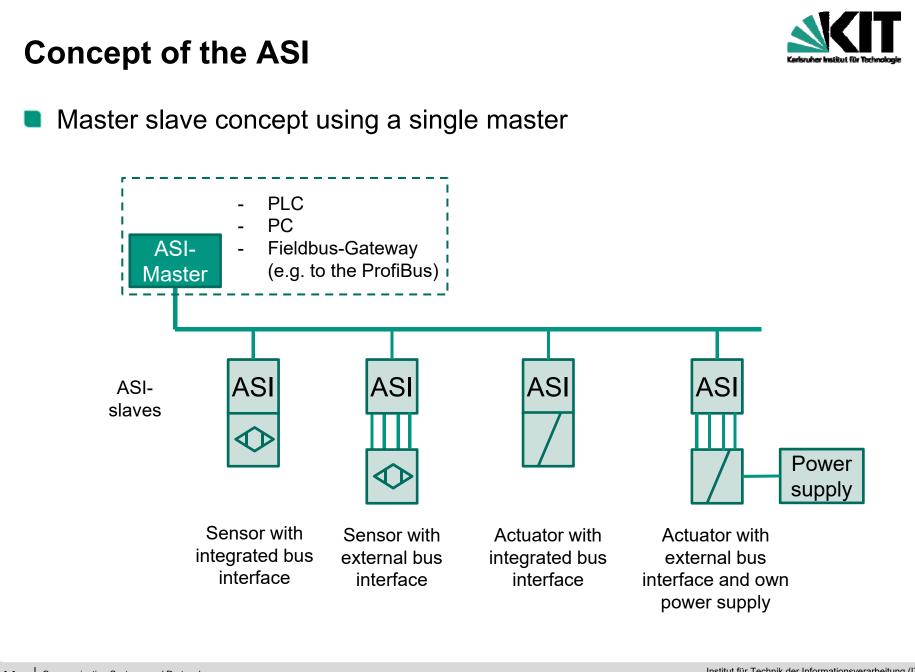

#### The Actuator Sensor Interface (ASI)

- The goal is to directly connect sensors/actuators to the control via a bus

- Requirements:

- Easy installation

- Easy commissioning and maintenance

- Low-priced (because of many bus connections)

- Data and energy should be transmitted on a two-conductor cable for all sensors and most actuators

- Simple and robust transmission procedure without limitations concerning net topology

- Compact and inexpensive bus connection

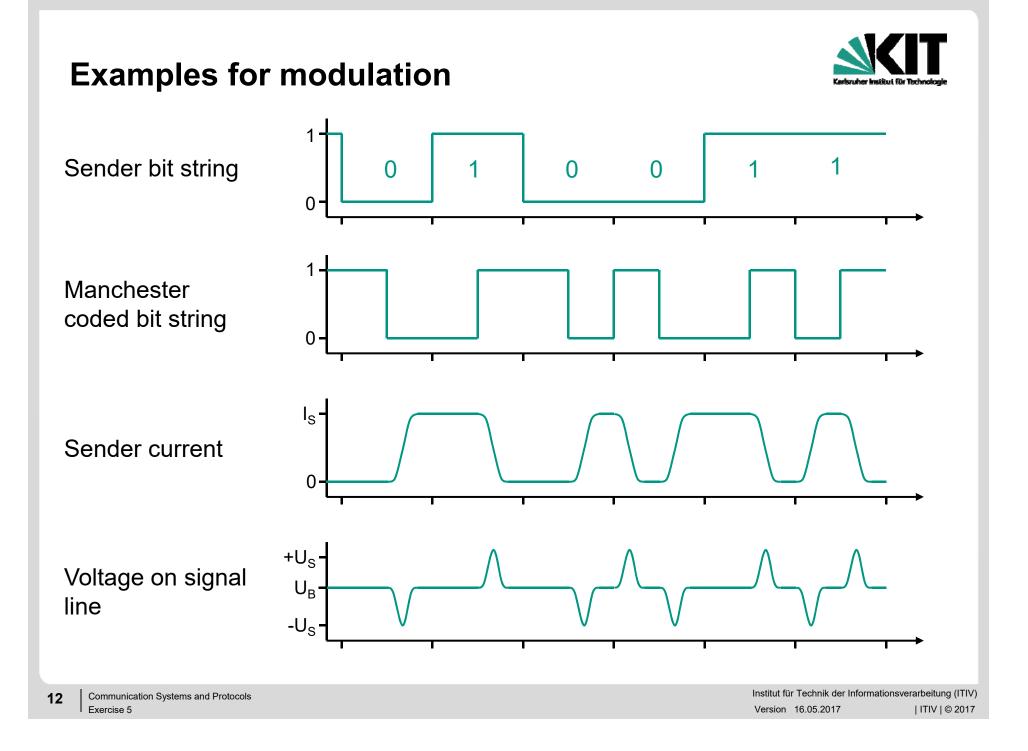

## Task 2: ASI

Institut für Technik der Informationsverarbeitung (ITIV) Version 07.07.2017 |© 2016

13 Communication Systems and Protocols Exercise 5

#### **FireWire**

- Multi Master System

- Self-Configuring

- Serial Bus System

- Hot-Plug Capability

- High Data rates

. . .

Real-time capability

**14** Communication Systems and Protocols Exercise 5

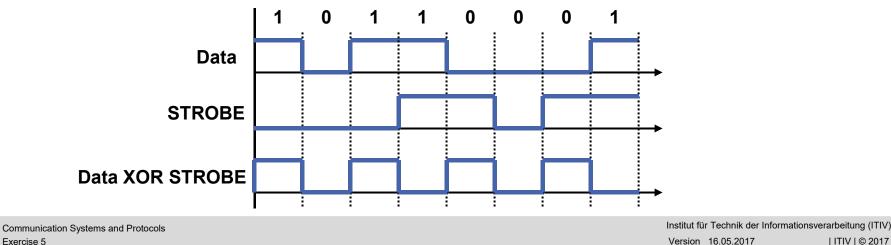

## Encoding

- Data is transmitted differential using two data lines

- NRZ coding

- No stuffing or other measures for clock recovery

- The STROBE signal is used to recover the clock signal

- When equal data bits are to be transmitted, the STROBE signal changes its state

- Recovery through XOR combination of both signals

- Advantages

- Insensitive for interference

- Lower bandwidth required

15

#### **Configuration of the bus**

- No user interaction for bus configuration required

- There is no dedicated controller, every bus member can become root of the tree

- Individual addresses and root of the bus is negotiated among the bus members

- Bus assignment is done in three steps

- Initialization

- Tree identification

- Self identification

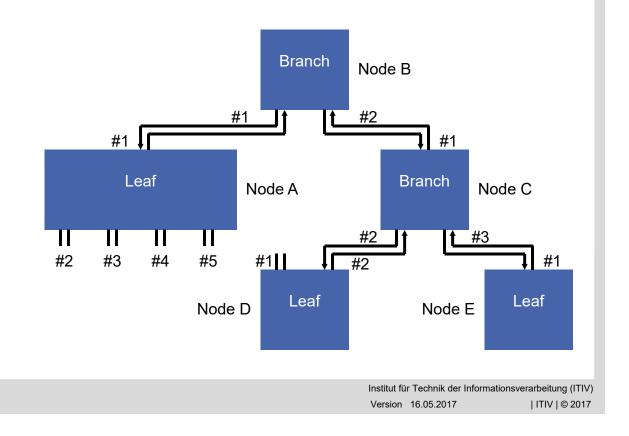

#### **1. Initialization**

- After a bus reset, every subscriber only knows the number of outgoing connections

- One single connection  $\rightarrow$  Leaf

- Several connections → Branch

- If the bus configuration changes another reset is issued

## 2. Tree identification

#### Method:

- 1. Every leaf sends a "parent-notify" packet on the bus and marks the corresponding port as "p" (parent)

- 2. The node that receives such a "parent-notify" packet will mark the corresponding port as "ch" (child)

- 3. If there is only one unmarked port left in a node, the node will send a "parent-notify" using the unmarked port and marks this port as parent

- 4. The node that has to wait the longest time, that in consequence has all ports root Node B marked as child, will become root of ch ch the tree #1 #1 р D Leaf Branch Node C Node A Waiting time and number off off off off ch ch П П of hops determine who #2 #3 #1 #4 #5 #1 will become root of the tree off Leaf Leaf Also a leaf can become Node D Node E root of the tree if it is waiting long enough Institut für Technik der Informationsverarbeitung (ITIV) **Communication Systems and Protocols** Version 16.05.2017 | ITIV | © 2017

## 3. Self identification

- Assigning the node address

- 1. Root transfers control to the node that is connected to the first port of the root

- 2. If this node has children on its own, he will forward control recursively to the first child node

- 3. When a leaf is reached, it will claim the next address that is available and sends a packet with its address and additional status information to the bus.

Leaf

Address 0

off

#4

off

П

#5

Node D

off

#3

off

#2

Root

Address 4

ch

Node A

#1

off

Leaf

Address 1

ch

Node B

- 4. After that, control is returned to the parent node that processes the next port

- 5. When a node has processed all of its children, it self-assigns an address and transfers control to #1 its parent node р

- Every node counts how many devices have already send their address and then chooses the next address available

- Thus the first leaf gets the address 0, while the root gets the highest address on the bus

Node C

#1

Leaf

Address 2

#1

ch

Node E

Branch

Address 3

# Task 3: Fire Wire

20 Communication Systems and Protocols Exercise 5 Institut für Technik der Informationsverarbeitung (ITIV) Version 07.07.2017 | ITIV | © 2017